## ELIZADE UNIVERSITY ILARA MOKIN, ONDO STATE

## **FACULTY OF ENGINEERING**

# DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

SECOND SEMESTER EXAMINATION, 2020/2021 ACADEMIC SESSION

COURSE TITLE: ELECTRONIC CIRCUIT I

**COURSE CODE: EEE 321**

**EXAMINATION DATE:** March 22, 2021

COURSE LECTURER: DR K. O. TEMIKOTAN

← HOD's Signature

TIME ALLOWED: 3 HOURS

#### INSTRUCTION

- 1. ANSWER ANY FIVE QUESTIONS

- 2. SEVERE PENALTIES APPLY FOR MISCONDUCT, CHEATING, POSSESSION OF UNAUTHORIZED MATERIALS DURING EXAM.

- 3. YOU ARE NOT ALLOWED TO BORROW ANY WRITING MATERIALS OR CALCULATORS DURING THE EXAMINATION.

- 4. SMART WATCHES OR SIMILAR DEVICES ARE NOT ALLOWED IN THE EXAMINATION VENUE.

## **QUESTION ONE**

- a. What is the drawback of a standard common emitter (CE) amplifier circuit? (2 marks)

- b. Using a neat diagram, show how a swamped CE amplifier is connected. (2 marks)

- c. What is the purpose of using a swamped connection? (1 mark)

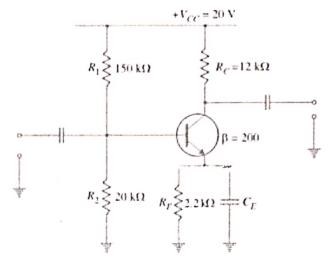

- d. For the amplifier circuit shown in Figure Q 4, find the voltage gain of the amplifier with (i) C<sub>E</sub> connected in the circuit (ii) C<sub>E</sub> removed from the circuit. Comment on the results. (7 marks)

Figure Q 1

## **QUESTION TWO**

- a. Using neat diagrams, show the difference between positive and negative feedback (4 marks)

- b. List four (4) advantages of negative feedback (2 marks)

- c. Show that voltage gain with negative feedback A<sub>vf</sub> is given by this expression:

$$A_{vf} = \frac{A_v}{(1 + m_v A_v)} \tag{6 marks}$$

## **QUESTION THREE**

- a. List four (4) common methods of biasing bipolar junction transistors. (2 marks)

- b. Design a base resistor bias circuit for a CE amplifier such that operating point is  $V_{CE}$  = 8V and  $I_{C}$  = 2 mA. You are supplied with a fixed 15V d.c. supply and a silicon transistor with  $\beta$  = 100. Take base-emitter voltage  $V_{BE}$  = 0.6V. (10 marks)

#### **OUESTION FOUR**

- a. What is the difference between tuned amplifiers and other amplifiers? (1 mark)

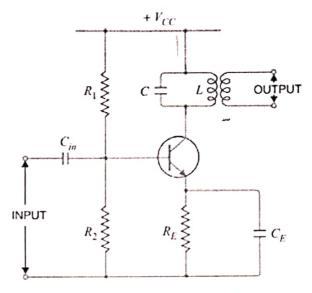

- b. For the tuned circuit shown in Figure Q 4, show that the resonant frequency is

$$f_r = \frac{1}{2\pi} \sqrt{\frac{1}{LC} - \frac{R^2}{L^2}}$$

(2 marks)

Figure Q 4 Tuned Amplifier Circut

- c. What is the resonant frequency if the resistance R of the inductor is so small that it can be ignored? (1 mark)

- d. Define quality factor of a tank circuit. (2 marks)

- e. Using a neat sketch of the impedance vs frequency curve show how the value of the resistance affect the impedance of the tuned amplifier. (2 marks)

- f. A parallel resonant circuit has a capacitor of 100 pF in one branch and inductance of 100  $\mu$ H plus a resistance of 10  $\Omega$  in parallel branch. If the supply voltage is 10 V, calculate (i) resonant frequency (ii) impedance of the circuit and (iii) line current at resonance. (4marks)

#### **QUESTION FIVE**

- a. List five (5) properties of operational amplifiers. (4 marks)

- b. A three-stage OP-amp circuit is required to provide voltage gains of +10, -18 and -27. Design the OP-amp circuit. Use a 270 k $\Omega$  feedback resistor for all three circuits. What output voltage will result for an input of 150  $\mu$ V? (8 marks)

### **QUESTION SIX**

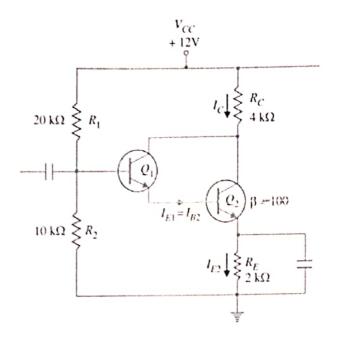

- a. List three (3) important properties of the Darlington amplifier. (2 marks)

- b. Draw a typical Darlington amplifier circuit showing the currents in the terminals (4 marks)

- c. For the Darlington amplifier in Figure Q 6, find (i) the d.c. levels of both transistors and (ii) a.c. emitter resistances of both transistors. (6 marks)

Figure Q 6

## QUESTION SEVEN

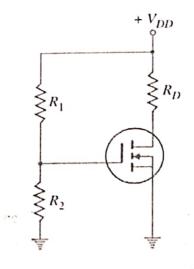

a. Figure Q 7 shows voltage divider biasing arrangement for n-channel E-MOSFET. The circuit components are R<sub>1</sub>, R<sub>2</sub>, and R<sub>D</sub>. Express (i) V<sub>GS</sub> (ii) V<sub>DS</sub> (iii) I<sub>D</sub> in terms of the supply voltage and the resistances in the circuit. (3 marks)

Figure Q 7 (i)

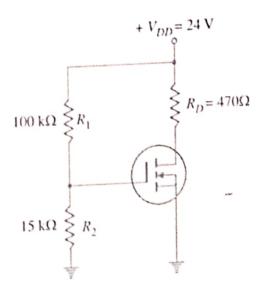

b. For the E-MOSFET circuit in Figure Q7(ii), determine (i)  $V_{GS}$ , (ii) the value of the constant K and (iii)  $V_{DS}$ .

The data sheet for this particular MOSFET gives  $I_{D \text{ (on)}} = 500 \text{ mA}$  at  $V_{GS} = 10 \text{V}$  and  $V_{GS \text{ (th)}} = 1 \text{ V}$ .

Figure Q 7 (ii)